Regression tool modify & log system

昨天演到RV64I執行時有遇到諸多bug,我們重新修改debug log及script來幫助我們更好的debug;現在的Script會跑一次,如果偵測到有錯誤則會將錯誤的log倒出來。

run_regression.py

import os

import sys

def run_aliss(folder_name, pattern_list_file):

with open(pattern_list_file, 'r') as file:

patterns = [line.strip() for line in file.readlines()]

if not os.path.exists(folder_name):

print("No file" + folder_name + "found")

return

for pattern in patterns:

aliss_command = f"./ALISS -e {folder_name}/{pattern}"

run_code = os.system(aliss_command)

if run_code != 0 : #check return value

aliss_command = f"./ALISS -e {folder_name}/{pattern} -d > {folder_name}_debug/{pattern}.log" #-d is new option to dump log

run_code = os.system(aliss_command)

if __name__ == "__main__":

if len(sys.argv) != 3:

print("python3 run_aliss.py folder_name pattern_list")

sys.exit(1)

folder_name = sys.argv[1]

pattern_list_file = sys.argv[2]

run_aliss(folder_name, pattern_list_file)

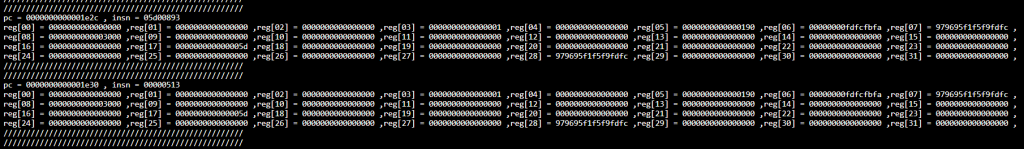

debug log 格式 example

原先的debug log資訊太少,我們增加每一道指令執行時將register內的結果印出來。

(最好的話要可以知道解出來是什麼指令,後面再加上這個功能。)

有了以上修正,配合objdump,我們可以很快的追到有哪些bug。

bug一覽

uint64_t shamt = imm & 0x1f; //[24:20]

在shift指令如sllw等,我們會將imm的5bit取出來當成shift amount,但實際上是取6bit,故更正。

=> imm & 0x3f; //[25:20]

reg[rd] = reg[rs1] <imm

在sltiu等set指令,我們將register的值讀出來與imm做比較,但這裡的imm要記得做sign-extension。

=> reg[rd] = (reg[rs1] < sext(imm,12))

reg[rd] = sext(reg[rs1] << reg[rs2]) & 0xffffffff,32)

在sllw等指令,我們會將shift的結果以32bit為單位存回暫存內,但實際上這邊的行為是將

rs1以32bit為單位,取rs2的最後5bit當成imm值,左移後再sign-extension。

=> reg[rd] = sext(((reg[rs1] & 0xffffffff) << (reg[rs2] & 0x1f)),32);

原先的sw/sh等function的寫法有誤,修改成以下程式碼

void set_mem_w(uint64_t addr, uint32_t data)

{

uint32_t* memory32 = (uint32_t*)(ALISS::memory + addr);

*memory32 = data;

return;

};

void set_mem_h(uint64_t addr, uint16_t data)

{

uint16_t* memory16 = (uint16_t*)(ALISS::memory + addr);

*memory16 = data;

return;

};

以上為rv64i遇到的所有bug,修正後risc-v test的rv64I全數通過,後續也會將這個script加到Jenkins regression flow內。

碎碎念 : 明天就是最後一天了orz,明天至少會讓目前IMA的三個test都全數通過,並嘗試去跑Linux,Linux要跑的話還會需要實現dtb load以及去設定一個位置為UART。